Qualcomm this morning is taking the wraps off of a new smartphone SoC for the mid-range market, the Snapdragon 7s Gen 3. The second of Qualcomm’s down-market ‘S’ tier Snapdragon 7 parts, the 7s series is functionally the entry-level tier for the Snapdragon 7 family – and really, most Qualcomm-powered handsets in North America.

With three tiers of Snapdragon 7 chips, the 7s can easily be lost in the noise that comes with more powerful chips. But the latest iteration of the 7s is a bit more interesting than usual, as rather than reusing an existing die, Qualcomm has seemingly minted a whole new die for this part. As a result, the company has upgraded the 7s family to use Arm’s current Armv9 CPU cores, while using bits and pieces of Qualcomm’s latest IPs elsewhere.

| Qualcomm Snapdragon 7-Class SoCs |

| SoC |

Snapdragon 7 Gen 3

(SM7550-AB) |

Snapdragon 7s Gen 3

(SM7635) |

Snapdragon 7s Gen 2

(SM7435-AB) |

| CPU |

1x Cortex-A715

@ 2.63GHz

3x Cortex-A715

@ 2.4GHz

4x Cortex-A510

@ 1.8GHz |

1x Cortex-A720

@ 2.5GHz

3x Cortex-A720

@ 2.4GHz

4x Cortex-A520

@ 1.8GHz |

4x Cortex-A78

@ 2.4GHz

4x Cortex-A55

@ 1.95GHz |

| GPU |

Adreno |

Adreno |

Adreno |

| DSP / NPU |

Hexagon |

Hexagon |

Hexagon |

Memory

Controller |

2x 16-bit CH

@ 3200MHz LPDDR5 / 25.6GB/s

@ 2133MHz LPDDR4X / 17.0GB/s |

2x 16-bit CH

@ 3200MHz LPDDR5 / 25.6GB/s

@ 2133MHz LPDDR4X / 17.0GB/s |

2x 16-bit CH

@ 3200MHz LPDDR5 / 25.6GB/s

@ 2133MHz LPDDR4X / 17.0GB/s |

| ISP/Camera |

Triple 12-bit Spectra ISP

1x 200MP or 64MP with ZSL

or

32+21MP with ZSL

or

3x 21MP with ZSL

4K HDR video & 64MP burst capture |

Triple 12-bit Spectra ISP

1x 200MP or 64MP with ZSL

or

32+21MP with ZSL

or

3x 21MP with ZSL

4K HDR video & 64MP burst capture |

Triple 12-bit Spectra ISP

1x 200MP or 48MP with ZSL

or

32+16MP with ZSL

or

3x 16MP with ZSL

4K HDR video & 48MP burst capture |

Encode/

Decode |

4K60 10-bit H.265

H.265, VP9 Decoding

Dolby Vision, HDR10+, HDR10, HLG

1080p120 SlowMo |

4K60 10-bit H.265

H.265, VP9 Decoding

HDR10+, HDR10, HLG

1080p120 SlowMo |

4K60 10-bit H.265

H.265, VP9 Decoding

HDR10, HLG

1080p120 SlowMo |

| Integrated Radio |

FastConnect 6700

Wi-Fi 6E + BT 5.3

2x2 MIMO |

FastConnect

Wi-Fi 6E + BT 5.4

2x2 MIMO |

FastConnect 6700

Wi-Fi 6E + BT 5.2

2x2 MIMO |

| Integrated Modem |

X63 Integrated

(5G NR Sub-6 + mmWave)

DL = 5.0 Gbps

5G/4G Dual Active SIM (DSDA) |

Integrated

(5G NR Sub-6 + mmWave)

DL = 2.9 Gbps

5G/4G Dual Active SIM (DSDA) |

X62 Integrated

(5G NR Sub-6 + mmWave)

DL = 2.9 Gbps

5G/4G Dual Active SIM (DSDA) |

| Mfc. Process |

TSMC N4P |

TSMC N4P |

Samsung 4LPE |

Officially, the Snapdragon 7s is classified as a 1+3+4 design – meaning there’s 1 prime core, 3 performance cores, and 4 efficiency cores. In this case, Qualcomm is using the same architecture for both the prime and efficiency cores, Arm’s current-generation Cortex-A720 design. The prime core gets to turbo as high as 2.5GHz, while the remaining A720 cores will turbo as high as 2.4GHz.

These are joined by the 4 efficiency cores, which, as is tradition, are based upon Arm’s current A5xx cores, in this case, A520. These can boost as high as 1.8GHz.

Compared to the outgoing Snapdragon 7s Gen 2, the switch in Arm cores represents a fairly significant upgrade, replacing an A78/A55 setup with the aforementioned A720/A520 setup. Notably, clockspeeds are pretty similar to the previous generation part, so most of the unconstrained performance uplift on this generation is being driven by improvements in IPC, though the faster prime core should offer a bit more kick for single-threaded workloads.

All told, touting a 20% improvement in CPU performance over the 7s Gen 2, though that claim doesn’t clarify whether it’s single or multi-threaded performance (or a mixture of both).

Meanwhile, graphics are driven by one of Qualcomm’s Adreno GPUs. As is usually the case, the company is not offering any significant details on the specific GPU configuration being used – or even what generation it is. A high-level look at the specifications doesn’t reveal any major features that weren’t present in other Snapdragon 7 parts. And Qualcomm isn’t bringing high-end features like ray tracing down to such a modest part. That said, I’ve previously heard through the tea leaves that this may be a next-generation (Adreno 800 series) design; though if that’s the case, Qualcomm is certainly not trying to bring attention to it.

Curiously, however, the video decode block on the SoC seems rather dated. Despite this being a new die, Qualcomm has opted not to include AV1 decoding – or, at least, opted not to enable it – so H.265 and VP9 are the most advanced codecs supported.

Compared to CPU performance gains, Qualcomm’s expected GPU performance gains are more significant. The company is claiming that the7s Gem 3 will deliver a 40% improvement in GPU performance over the 7s Gen 2.

Finally, the Hexagon NPU block on the SoC incorporates some of Qualcomm’s latest IP, as the company continues their focused AI push across all of their chip segments. Notably, the version of the NPU used here gets INT4 support for low precision client inference, which is new to the Snapdragon 7s family. As with Qualcomm’s other Gen 3 SoCs, the big drive here is for local (on-device) LLM execution.

With regards to performance, Qualcomm says that customers should expect to see a 30% improvement in AI performance relative to the 7s Gen 2.

Feeding all of these blocks is a 32-bit memory controller. Interestingly, Qualcomm has opted to support older LPDDR4X even with this newer chip, so the maximum memory bandwidth depends on the memory type used. For LPDDR4X-4266 that will be 17GB/sec, and for LPDDR5-6400 that will be 25.6GB/sec. In both cases, this is identical to the bandwidth available for the 7s Gen 2.

Rounding out the package, the 7s Gen 3 does incorporate some newer/more powerful camera hardware as well. We’re still looking at a trio of 12-bit Spectra ISPs, but the maximum resolution in zero shutter lag and burst modes has been bumped up to 64MPix. Video recording capabilities are otherwise identical on paper, as the 7s Gen 2 already supported 4K HDR capture.

Meanwhile on the wireless communication side of matters, the 7s Gen 3 packs one of Qualcomm’s integrated Snapdragon 5G modems. As with its predecessor, the 7s Gen 3 supports both Sub-6 and mmWave bands, with a maximum (theoretical) throughput of 2.9Gbps.

Eagle-eyed chip watchers will note, however, that Qualcomm is doing away with any kind of version information as of this part. So while the 7s Gen 2 used a Snapdragon X62 modem, the 7s Gen 3’s modem has no such designation – it’s merely an integrated Snapdragon modem. According to the company, this change has been made to “simplify overall branding and to be consistent with other IP blocks in the chipset.”

Similarly, the Wi-Fi/Bluetooth block has lost its version number; it is now merely a FastConnect block. In regards to features and specifications, this appears to be the same Wi-Fi 6E block that we’ve seen in half a dozen other Snapdragon SoCs, offering 2 spatial streams at channel widths up to 160MHz. It is worth noting, however, that since this is a newer SoC it’s certified for Bluetooth 5.4 support, versus the 5.2/5.3 certification other Snapdragon 7 chips have carried.

Finally, the Snapdragon 7s Gen 3 itself is being built on TSMC’s N4P process, the same process we’ve seen the last several Qualcomm SoCs use. And with this, Qualcomm has now fully migrated the entire Snapdragon 8 and Snapdragon 7 lines off of Samsung’s 4nm process nodes; all of their contemporary chips are now built at TSMC. And like similar transitions in the past, this shift in process nodes is coming with a boost to power efficiency. While it’s not the sole cause, overall Qualcomm is touting a 12% improvement in power savings.

Wrapping things up, Qualcomm’s launch customer for the Snapdragon 7s Gen 3 will be Xiaomi, who will be the first to launch a new phone with the chip. Following them will be many of the other usual suspects, including Realme and Sharp, while the much larger Samsung is also slated to use the chip at some point in the coming months.

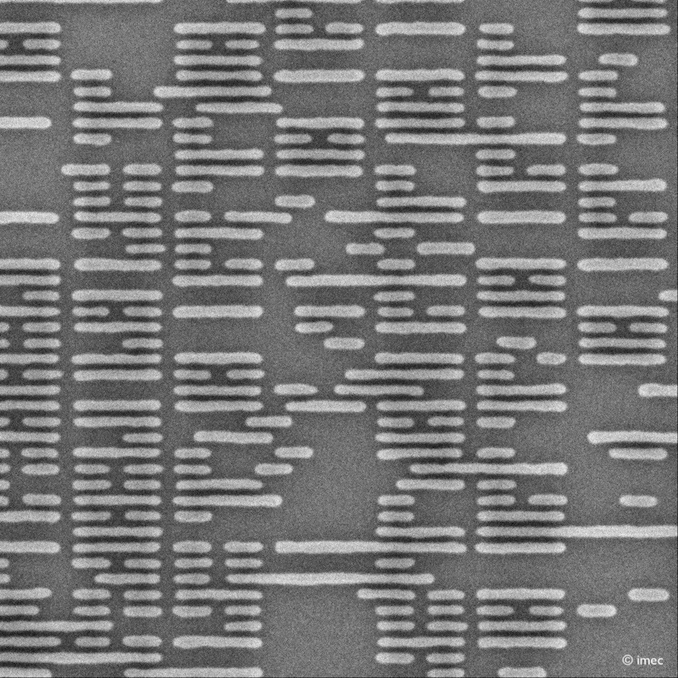

%20after%20pattern%20transfer_thumb.png)